Samsung to Use In-House Chip for Its Next Galaxy Series

According to media reports, Samsung decided to use its Exynos 2600 chip across the Galaxy S26 series in selected markets.

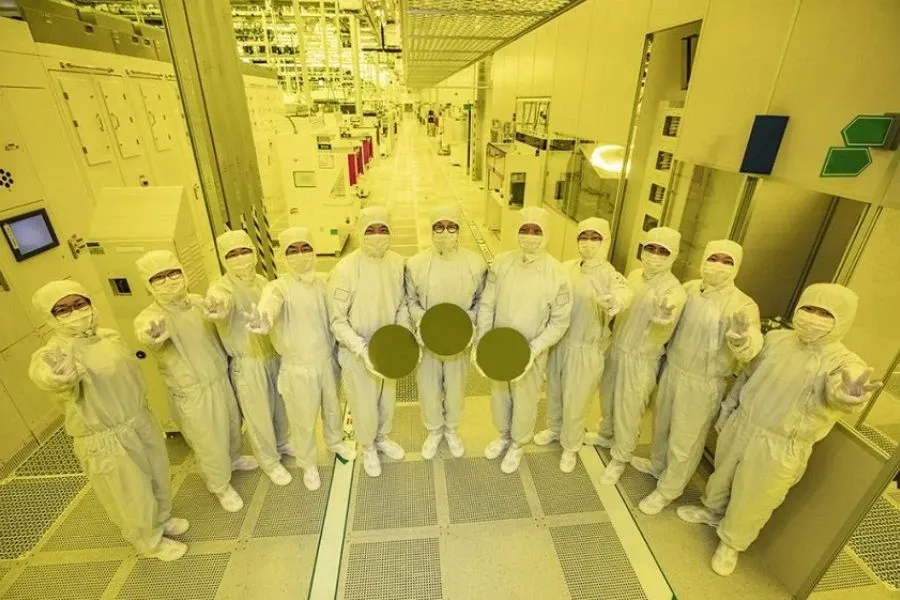

Samsung has started the initial production of its 3-nanometer (nm) process node applying Gate-All-Around (GAA) transistor architecture. Multi-Bridge-Channel FET (MBCFET), Samsung’s GAA technology implemented for the first time, defies the performance limitations of FinFET, improving power efficiency by reducing the supply voltage level, while also enhancing performance by increasing drive current capability. Samsung is starting the first application of the nanosheet transistor with semiconductor chips for high-performance, low-power computing applications and plans to expand to mobile processors.

“Samsung has grown rapidly as we continue to demonstrate leadership in applying next-generation technologies to manufacturing, such as the foundry industry’s first High-K Metal Gate, FinFET, as well as EUV. We seek to continue this leadership with the world’s first 3nm process with the MBCFET™,“ said Siyoung Choi, President and Head of Foundry Business at Samsung. “We will continue active innovation in competitive technology development and build processes that help expedite achieving maturity of the technology.“

Samsung’s proprietary technology utilizes nanosheets with wider channels, which allow higher performance and greater energy efficiency compared to GAA technologies using nanowires with narrower channels. Utilizing the 3nm GAA technology, Samsung will be able to adjust the channel width of the nanosheet to optimize power usage and performance to meet various customer needs.

In addition, the design flexibility of GAA is highly advantageous for Design Technology Co-Optimization (DTCO), which helps boost Power, Performance, Area (PPA) benefits. Compared to the 5nm process, the first-generation 3nm process can reduce power consumption by up to 45%, improve performance by 23% and reduce the area by 16% compared to 5nm, while the second-generation 3nm process is to reduce power consumption by up to 50%, improve performance by 30% and reduce the area by 35%.